# NEC's LOW POWER GPS RF RECEIVER

**UPB1008K**

#### **FEATURES**

- LOW POWER CONSUMPTION: 52 mW

- DUAL-CONVERSION IQ DOWN CONVERTER<sup>1</sup>: Reference frequency: REFin = 27 MHz

- PSEUDO-BASEBAND WITH 2-BIT DIGITIZED OUTPUT

- ON-CHIP LNA, ON-CHIP FREQUENCY SYNTHESIZER, IF AGC AMPLIFIER:

with 45 dB typical range of adjustable gain

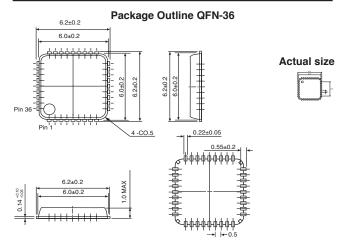

SMALL 36 PIN QFN PACKAGE:

Flat lead style for better RF performance

Note:

1. Based on eRide's proprietary GPS DSP architecture

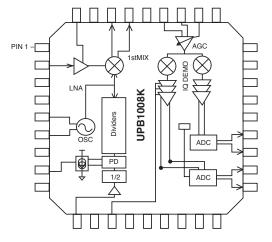

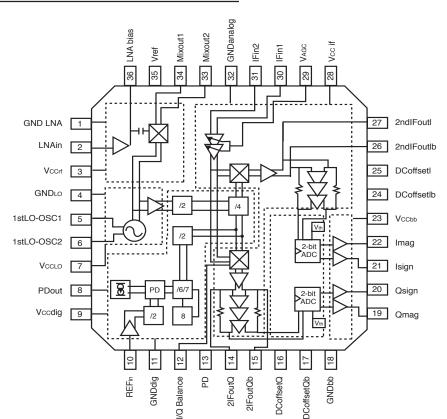

### **BLOCK DIAGRAM**

#### **APPLICATIONS**

- E911 ENABLED MOBILE PHONE

- IN-VEHICLE NAVIGATION SYSTEMS

- LOW POWER HANDHELD GPS RECEIVER

- PC/PDA+GPS INTEGRATION

- ASSET TRACKING

### DESCRIPTION

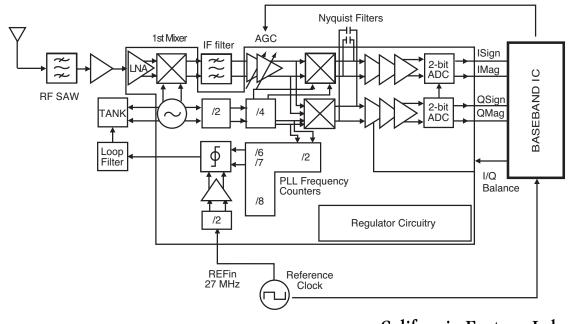

NEC's UPB1008K is a Silicon RFIC especially designed for handheld low power/low cost GPS receivers. The IC combines an LNA, followed by a double-conversion RF/IF downconverter block and a PLL frequency synthesizer on one chip. The second IF Freqency is a pseudo- baseband signal into a on-chip 2-bit A/D converters. The device can operate on a supply voltage as low as 2.7 V, and is a housed in a small 36 pin QFN (Quad, Flat, No-lead) package, resulting in a very low power consumption and reduced board space.

NEC's stringent quality assurance and test procedures ensure the highest reliability and performance.

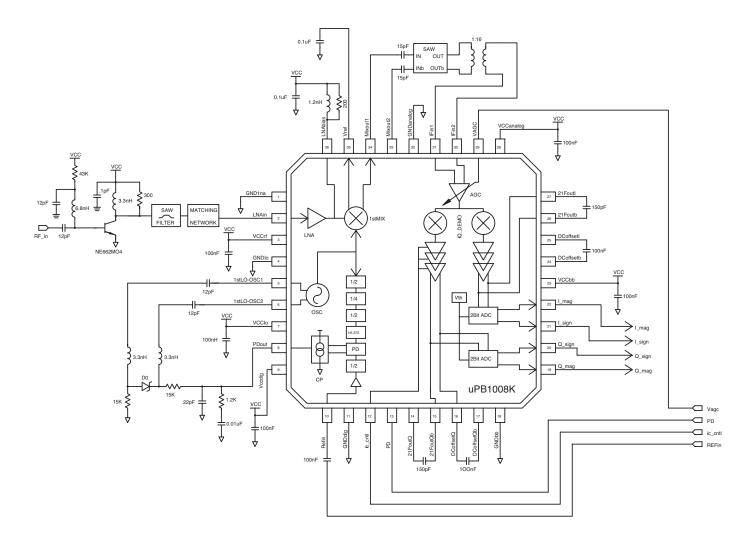

# **RF APPLICATION DIAGRAM**

California Eastern Laboratories

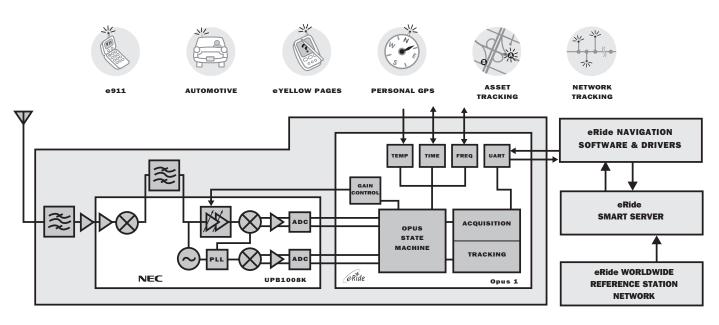

### ADVANCED GPS COMPLETE SOLUTION

### ADVANCED GPS COMPLETE SOLUTION

"NEC Corporation and eRide, Inc. have teamed to provide an advanced positioning solution delivering high GPS performance, accuracy, integration and architecture flexibility. The chip set combines CEL's **UPB1008K** receiver IC with eRide's **Opus One** SOC (System-on-a-Chip) Baseband ASIC and is suitable for standard GPS products as well as Cellular Handset applications. Also provided are scalable client navigation software and drivers, plus location-aiding data from eRide's Smart Server. Together, they offer a complete hardware/infrastructure solution.

The chip set's design allows it to operate independently of wireless interface standards - and independently of the host product's CPU and Operating System. This unique approach to system integration makes it easy to deploy the chip set into an wireless application, in any wireless network. A "Universal Hardware" solution, the design promises lower manufacturing costs and, ultimately lower cost to the consumer.

The chip set's advanced positioning architecture offers unmatched sensitivity providing fast, accurate positioning architecture offers unmatched sensitivity providing fast and accurate position fixes, even when indoors or in deep in urban canyons."

# HIGH PERFORMANCE GPS OMNI MODE

#### LI, C/A code receiver

| Performance                  | Indoor         | Outdoor              |

|------------------------------|----------------|----------------------|

| Time to First Fix w/ aiding  | 5-7sec         | 1-3sec               |

| Time to First Fix w/o aiding | 10-20sec       | 3-5sec               |

| Accuracy                     | 10-25m cep     | 2-5m cep             |

| Sensitivity                  | -155dBm        | -142dBm              |

|                              | in 1sec dwells | in two 10msec dwells |

Superior performance in high reflection indoor environments and in urban canyon types of outdoor environments

#### **POWER DISSIPATION**

| First Fix | 400 mW     |

|-----------|------------|

| Tracking  | 200-300 mW |

| Stand By  | 30 mW      |

# ELECTRICAL CHARACTERISTICS (TA = 25°C, Vcc = 3.0 V, unless otherwise specified)

| SYMBOLS | PARAMETERS AND CONDITIONS                                   | UNITS | MIN | ТҮР | MAX  |

|---------|-------------------------------------------------------------|-------|-----|-----|------|

| lcc     | Total Circuit Current, No Signals                           | mA    | 14  | 18  | 23.5 |

| Vcc     | Supply Voltage                                              | V     | 2.7 | 3.0 | 3.3  |

| ICC_PD  | Power down current, PIN 13 = VIL                            | μΑ    | -   | 1   | 10   |

| lcc rf  | RF Block Circuit Current (pin 3), No signal                 | μΑ    | 0.4 | 0.5 | 0.7  |

| lcc lo  | VCO Block Circuit Current (pin 7), No signal                | mA    | 4.1 | 5.6 | 7.2  |

| ICC pll | PLL Block Circuit Current (pin 9), No signal                | mA    | 2.7 | 3.6 | 4.7  |

| ICC bb  | Baseband Block Circuit Current (pin 23), No signal,         | mA    | 2.5 | 3.4 | 4.3  |

|         | open load                                                   |       |     |     |      |

| ICC if  | IF Block Circuit Current (pin 28) , No signal               | mA    | 2.7 | 3.7 | 4.7  |

| ICC Ina | Pre-Amplifier Open Connector Current (pin 36),<br>No signal | mA    | 1.0 | 1.4 | 1.8  |

#### LNA/RF DOWNCONVERTER

(fRFin = 1575.42 MHz, f1stLOin = 1400 MHz, PLO = -10 dBm, f1stIF = 175 MHz, Pin 13: VIL = 3 V, ZL differential = 32Ω & Zs = Γopt)

| SYMBOLS     | PARAMETERS AND CONDITIONS                                              | UNITS | MIN | ТҮР | MAX |

|-------------|------------------------------------------------------------------------|-------|-----|-----|-----|

| CGLNA_MIX   | Power conversion gain from 2nd LNA/mixer to 1st IF,<br>PRFin = -50 dBm | dB    | 18  | 23  | 28  |

| NFlna_mix   | Noise Figure of 2nd LNA/mixer(SSB), Input matched                      | dB    | _   | 5   | -   |

| P1dBLNA_MIX | 1 dB Compression refer to source, Input matched                        | dBm   | -   | -38 | -   |

| ZLNAin      | RF Input Impedance of LNA                                              | Ohm   | -   | 31  | -   |

| ZMIXout     | IF Output Impedance of Mixer                                           | Ohm   |     | 32  |     |

| Alo-IF      | Local Signal Leak to IF, f1stLOin=1400 MHz,<br>PLO = 0 dBm             | dBm   | _   | -35 | -   |

| Alo-RF      | Local Signal Leak to RF, f1stLOin=1400 MHz,<br>PLO = 0 dBm             | dBm   | _   | -50 | _   |

#### PLL

| SYMBOLS | PARAMETERS AND CONDITIONS                          | UNITS | MIN | ТҮР  | MAX |

|---------|----------------------------------------------------|-------|-----|------|-----|

| Ісрон   | PLL Charge Pump High Side Current @ VCPout = VCC/2 | μΑ    | -   | 200  | -   |

| ICPOL   | PLL Charge Pump Low Side Current @ VCPout = VCC/2  | μΑ    | -   | -200 | -   |

| fpd     | Phase Comparison Frequency                         | MHz   | -   | 13.5 | -   |

#### CRYSTAL OSCILLATOR/REVERENCE AMPLIFIER BLOCK

| SYMBOLS | PARAMETERS AND CONDITIONS                          | UNITS  | MIN | ТҮР | MAX |

|---------|----------------------------------------------------|--------|-----|-----|-----|

| VREFin  | Reference input minimum level                      | mVpp   | 50  | 200 | -   |

| fref    | Input Frequency of Reference Input                 | MHz    | _   | 27  | -   |

| VT      | VCO Control Voltage, PLL Locked                    | V      | 0.8 | 1.5 | 2.2 |

| C/N     | VCO C/N, $\triangle$ 1kHz, Loop band width = 5 kHz | dBc/Hz | 57  | 62  | _   |

AGC AMPLIFIER, I-Q DEMODULATOR, and ADC BLOCK(f1stlFin = 175 MHz, Zin = 600Ω)

| 71010 71111 |                                                                                                        | = 170 10112, 21 | = = = = = = = = = = = = = = = = = = = = |     |     |

|-------------|--------------------------------------------------------------------------------------------------------|-----------------|-----------------------------------------|-----|-----|

| SYMBOLS     | PARAMETERS AND CONDITIONS                                                                              | UNITS           | MIN                                     | TYP | MAX |

| CGAGC/MIX   | Maximum voltage conversion gain of AGC amplifier/<br>I-Q mixer, Pin = -60 dBm, VAGC = 0.5 V, Unmatched | dB              | _                                       | 30  | _   |

|             | Minimum voltage conversion gain of AGC amplifier/<br>I-Q mixer, Pin = -60 dBm, VAGC = 2.0 V, Unmatched | dB              | _                                       | -15 | _   |

| AAGC/MIX    | AGC control range, $V_{AGC} = 0.5 V$ to 2 V                                                            | dB              | 25                                      | 45  | -   |

| P1dBAGC     | 1 dB compression input to AGC amplifier,<br>set voltage gain = 30 dB                                   | dBm             | -                                       | -45 | -   |

| VAGC        | AGC control voltage                                                                                    | V               | 0.5                                     | -   | 2.0 |

| BW          | 3dB Mixer Bandwidth                                                                                    | MHz             | _                                       | 10  | _   |

| VIQ-C       | IQ BalanceControl Voltage, Gain(Ich) = Gain (Qch)                                                      | V               | -                                       | 2.1 | 2.8 |

| Alq-c       | IQ Balance Control Gain Range, VIQ-C = 0 to 3 V                                                        | dB              | 4.0                                     | 6.5 | -   |

| Duty<br>Ich | Ich Mag Bit Output Pulse Duty, P1stIFin = -84 dBm<br>VAGC = 0.5 V, VIQ-C = 0 V                         | %               | 50                                      | -   | _   |

| Duty<br>Qch | Qch Mag Bit Output Pulse Duty, PIF2in = -88 dBm<br>VAGC = 0.5 V, VIQ-C = 0 V                           | %               | 50                                      | -   | _   |

| BASEBA      | <b>ND AMPLIFIER BLOCK</b> (Zs = $2k\Omega \& ZL = 2 k\Omega$ )                                         |                 |                                         |     |     |

| SYMBOLS     | PARAMETERS AND CONDITIONS                                                                              | UNITS           | MIN                                     | ТҮР | MAX |

| Vввон       | Baseband output logic high, CL = 10 pF                                                                 | V               | 2.0                                     | _   | _   |

| VBBOL       | Baseband output logic low, CL = 10 pF                                                                  | V               | 0                                       | _   | 0.5 |

|             |                                                                                                        |                 |                                         |     |     |

# ABSOLUTE MAXIMUM RATINGS<sup>1,2</sup> (TA = 25°C)

| SYMBOLS   | PARAMETERS                           | UNITS | RATINGS     |

|-----------|--------------------------------------|-------|-------------|

| Vcc       | Supply Voltage <sup>4</sup>          | Vcc   | 3.6         |

| PD        | Total Power Dissipation <sup>3</sup> | mW    | 361         |

| Тор       | Operating Temperature                | °C    | -40 to +85  |

| Тѕтс      | Storage Temperature                  | °C    | -55 to +150 |

| ICC_total | Total Circuit Current <sup>4</sup>   |       |             |

#### Notes:

1. Operation in excess of any one of these parameters may result in permanent damage.

- 2. More than two items must not be reached simultaneously.

- 3. TA =  $+85^{\circ}$ C, mounted on a 50 x 50 x 1.6 mm double-sided copper clad epoxy glass PWB.

- 4. TA = 25°C

#### RECOMMENDED OPERATING CONDITIONS

| SYMBOLS          | PARAMETERS             | UNITS | MIN | TYP  | MAX |

|------------------|------------------------|-------|-----|------|-----|

| Vcc              | Supply Voltage         | V     | 2.7 | 3.0  | 3.3 |

| Тор              | Operating Temperature  | °C    | -40 | +25  | +85 |

| fRFin            | RF Input Frequency     | MHz   |     | 1575 |     |

| fREFin           | Reference Frequency    | MHz   |     | 27   |     |

| f1st∟o           | 1st LO Oscillating     |       |     |      |     |

|                  | Frequency              | MHz   |     | 1400 |     |

| <b>f</b> 1stIFin | 1st IF Input Frequency | MHz   |     | 175  |     |

| f2ndLOin         | 2nd LO Input Frequency | MHz   |     | 175  |     |

| VIH              | Power Down Control     |       |     |      |     |

|                  | Voltage "High"         | V     | 2   |      | Vcc |

| VIL              | Power Down Control     |       |     |      |     |

|                  | Voltage "Low"          | V     | 0   |      | 0.5 |

# **APPLICATION CIRCUIT**

# UPB1008K

| Pin No. | Symbol     | Function and Application                                                                                                                                                 | Internal Equivalent Circuit                                                                                |

|---------|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------|

| 1       | GNDIna     | Ground pin of LNA                                                                                                                                                        | 30                                                                                                         |

| 2       | LNAin      | Input pin of low noise amplifier. It is a<br>single-ended open collector design.<br>Capacitive coupling is required; external<br>matching will improve gain or NF.       |                                                                                                            |

| 3       | VCCrf      | Supply voltage pin of LNA, RF mixer and VCO voltage regulator.                                                                                                           | 70                                                                                                         |

| 4       | GNDIo      | Ground pin of 1st LO Oscillator circuit and RF Mixer.                                                                                                                    |                                                                                                            |

| F       | 1stLO-OSC1 | Din 5 % 6 are base size of the differential                                                                                                                              |                                                                                                            |

| 5<br>6  | 1stLO-OSC1 | Pin 5 & 6 are base pins of the differential<br>amplifier for 1st LO oscillator. These pins<br>require an LC (varacator) tank circuit to<br>oscillate at around 1400 MHz. |                                                                                                            |

| 7       | VCClo      | Supply voltage pin of oscillator circuit for<br>1st LO Oscillator and RF mixer                                                                                           | Regulator<br>GND<br>4                                                                                      |

| 8       | PDout      | This is a current mode charge pump output.<br>For connection to a passive RC loop filter for driving<br>external varactor diode of 1stLO-OSC.                            | Source Control B OL CALL                                                                                   |

| 9       | VCCdig     | Supply voltage pin of digital portion of the chip.                                                                                                                       | Ga Sink Control                                                                                            |

| 10      | REFin      | Input pin of reference frequency buffer. This pin<br>should be equipped with external 27 MHz<br>oscillator (e.g. TCXO).                                                  | 9 <b>9</b><br><b>1</b><br><b>1</b><br><b>1</b><br><b>1</b><br><b>1</b><br><b>1</b><br><b>1</b><br><b>1</b> |

| 11      | GNDdig     | Ground pin of digital portion of the chip.                                                                                                                               | 10<br>10<br>10<br>10<br>10<br>10<br>10<br>10<br>10<br>10                                                   |

| Pin No.         | Symbol                      | Function and Application                                                                                                                                                                     | Internal Equivalent Circuit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|-----------------|-----------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 12              | I/Q Balance<br>Control      | The voltage on this pin controls the Q channel<br>IF Amplifier Gain. Gain control of ±2 dB can be<br>achieved for 0~3 V.<br>Leave open-circuited if not used.                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 13              | PD1                         | Standby mode control.<br>Low=whole chip OFF & High=Whole chip ON.                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| <u>14</u><br>15 | 2IFout-Q<br>2IFout-Qb       | Differential ouptut pins of quadrature demodulator<br>Q output. Adding a lowpass shunt capacitor<br>between these pins will define the IF Bandwidth.                                         | average of the second s |

| 16              | DC offset Q<br>DC offset Qb | DC offset compensation pin for C arm. A low pass<br>capacitor shunt to Pin 17 is required.<br>DC offset compensation pin for Q-bar arm.<br>A low pass capacitor shunt to Pin 16 is required. | Production of the second secon |

# **UPB1008K**

| Pin No.  | Symbol             | Function and Application                                                                                                                                                                        | Internal Equivalent Circuit                                                                     |

|----------|--------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------|

| 18<br>19 | GNDbb<br>Qmag      | Ground pin of CMOS output driver.<br>Digitized Q signal. Magnitude bit of 2-bit ADC output.                                                                                                     | 230                                                                                             |

| 20       | Qinag<br>Qsign     | Digitized Q signal. Sign bit of 2-bit ADC output.                                                                                                                                               |                                                                                                 |

| 20       |                    | Digitized & Signal. Sign bit of 2-bit ADC output.                                                                                                                                               | ¥ r=21.5                                                                                        |

|          | Isign              |                                                                                                                                                                                                 | 1 1 1                                                                                           |

| 22<br>23 | Imag<br>VCCbb      | Digitized I signal. Magnitude bit of 2-bit ADC output.<br>Supply voltage pin of CMOS output driver.                                                                                             | L 2021.22)                                                                                      |

| 24       | DCoffsetIb         | DC offset compensation pin for I-bar arm.<br>A low pass capacitor shunt to Pin 25 is required.                                                                                                  | See pin 16 & 17 schematic                                                                       |

| 25       | DCoffsetI          | DC offset compensation pin for I arm.<br>A low pass capacitor shunt to Pin 24 is required.                                                                                                      |                                                                                                 |

| 26       | 2IFout-Ib          | Differential output pins of quadrature                                                                                                                                                          | See pin 14 & 15 schematic                                                                       |

| 27       | 2IFout-I           | demodulator I output. Adding a lowpass shunt<br>capacitor between these pins will define the<br>IF bandwidth.                                                                                   |                                                                                                 |

| 28       | VCC if             | Supply voltage pin of analog portion of the chip.                                                                                                                                               | 28 🔿                                                                                            |

| <br>     | IF-in1<br>IF-in2   | Gain control voltage pin of IF amplifier. This voltage<br>performs reverse control,(i.e., VAGC up $\rightarrow$ gain down).<br>If this pin is left open, then it is default at<br>maximum gain. | 23<br>23<br>23<br>24<br>7 = 300<br>7 = 300<br>7 = 300<br>7 = 3k<br>1 = 3k<br>23<br>24<br>7 = 3k |

| 32       | GNDanalog          | Ground pin of analog portion of the chip.                                                                                                                                                       |                                                                                                 |

| 33<br>34 | Mixout2<br>Mixout1 | Differential output pins of RF mixer. This is an emitter follower output buffer, provide a 50Ω output load.                                                                                     | Tespulator                                                                                      |

| Pin No. | Symbol  | Function and Application                                                                                                                                  | Internal Equivalent Circuit                                                                 |  |

|---------|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------|--|

| 35      | Vref    | Base-emitter junction voltage wth respect to ground.<br>May be used for biasing an external discrete<br>transistor. Regulation will develop PTAT current. | Regulator<br>GND<br>4 0<br>1 |  |

| 36      | LNAbias | LNA output pin. External bias (Vcc) and matching for gain is required.                                                                                    | See pin 2 schematic                                                                         |  |

### **INTERNAL BLOCK DIAGRAM**

#### ORDERING INFORMATION

| Part Number | Package            |

|-------------|--------------------|

| UPB1008K-A  | 36 Pin plastic QFN |

#### OUTLINE DIMENSIONS (Units in mm)

#### Caution:

The island pins located on the corners are needed to fabricate products in our plant, but do not serve any other function.

Consequently the island pins should not be soldered and should remain non-connection pins.

Life Support Applications

These NEC products are not intended for use in life support devices, appliances, or systems where the malfunction of these products can reasonably be expected to result in personal injury. The customers of CEL using or selling these products for use in such applications do so at their own risk and agree to fully indemnify CEL for all damages resulting from such improper use or sale.

California Eastern Laboratories, Your source for NEC RF, Microwave, Optoelectronic, and Fiber Optic Semiconductor Devices. 4590 Patrick Henry Drive • Santa Clara, CA 95054-1817 • (408) 988-3500 • FAX (408) 988-0279 • www.cel.com DATA SUBJECT TO CHANGE WITHOUT NOTICE

Subject: Compliance with EU Directives

CEL certifies, to its knowledge, that semiconductor and laser products detailed below are compliant with the requirements of European Union (EU) Directive 2002/95/EC Restriction on Use of Hazardous Substances in electrical and electronic equipment (RoHS) and the requirements of EU Directive 2003/11/EC Restriction on Penta and Octa BDE.

CEL Pb-free products have the same base part number with a suffix added. The suffix –A indicates that the device is Pb-free. The –AZ suffix is used to designate devices containing Pb which are exempted from the requirement of RoHS directive (\*). In all cases the devices have Pb-free terminals. All devices with these suffixes meet the requirements of the RoHS directive.

This status is based on CEL's understanding of the EU Directives and knowledge of the materials that go into its products as of the date of disclosure of this information.

| Restricted Substance<br>per RoHS | Concentration Limit per RoHS<br>(values are not yet fixed) | Concentration contained<br>in CEL devices |            |

|----------------------------------|------------------------------------------------------------|-------------------------------------------|------------|

| Lead (Pb)                        | < 1000 PPM                                                 | -A<br>Not Detected                        | -AZ<br>(*) |

| Mercury                          | < 1000 PPM                                                 | Not Detected                              |            |

| Cadmium                          | < 100 PPM                                                  | Not Detected                              |            |

| Hexavalent Chromium              | < 1000 PPM                                                 | Not Detected                              |            |

| РВВ                              | < 1000 PPM                                                 | Not Detected                              |            |

| PBDE                             | < 1000 PPM                                                 | Not Detected                              |            |

If you should have any additional questions regarding our devices and compliance to environmental standards, please do not hesitate to contact your local representative.

In no event shall CEL's liability arising out of such information exceed the total purchase price of the CEL part(s) at issue sold by CEL to customer on an annual basis.

See CEL Terms and Conditions for additional clarification of warranties and liability.

Important Information and Disclaimer: Information provided by CEL on its website or in other communications concerting the substance content of its products represents knowledge and belief as of the date that it is provided. CEL bases its knowledge and belief on information provided by third parties and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. CEL has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. CEL and CEL suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.